IBM et Advanced Micro Devices (AMD) ont co-développé une nouvelle méthode pour mettre en oeuvre la technologie "strained silicon". La technique, baptisée "Dual Stress Liner" (DSL), devrait permettre aux deux sociétés de doper les performances de leurs puces dčs le premier semestre. Alors qu'il devient de plus en plus difficile d'accroître la performance de leurs puces par simple réduction de la taille des transistors, les fondeurs mettent en oeuvre des techniques alternatives. La technologie "strained silicon" consiste ŕ étirer ou ŕ compresser les atomes de silicium afin d'améliorer la circulation des électrons. Schématiquement, les transistors P (positif) fonctionnent mieux lorsqu'ils sont compressés, tandis que les transistors N (négatif) donnent leur meilleur lorsqu'ils sont étirés. Toute l'astuce de la technologie DSL d'IBM et d'AMD est de s'assurer que la "compression" des atomes de silicium ne s'effectue qu'aux emplacements des transistors P et que l'étirement n'affecte que les transistors N... La technique devrait ętre utilisée dčs le premier semestre par AMD pour produire des Opteron et des Athlon 64 plus performants (environ 25%) sans augmentation de consommation électrique. IBM prévoit aussi de l'appliquer au premier semestre a sa gamme de processeurs Power dont les puces PowerPC 970 (G5 chez Apple).

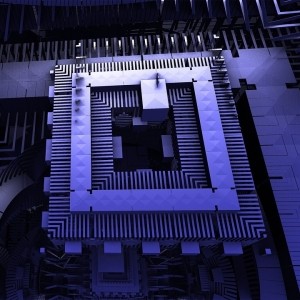

IBM et AMD travaillent ensemble à l'amélioration des performances des transistors

Articles les plus lus

Suivez-nous